PLL の仕様

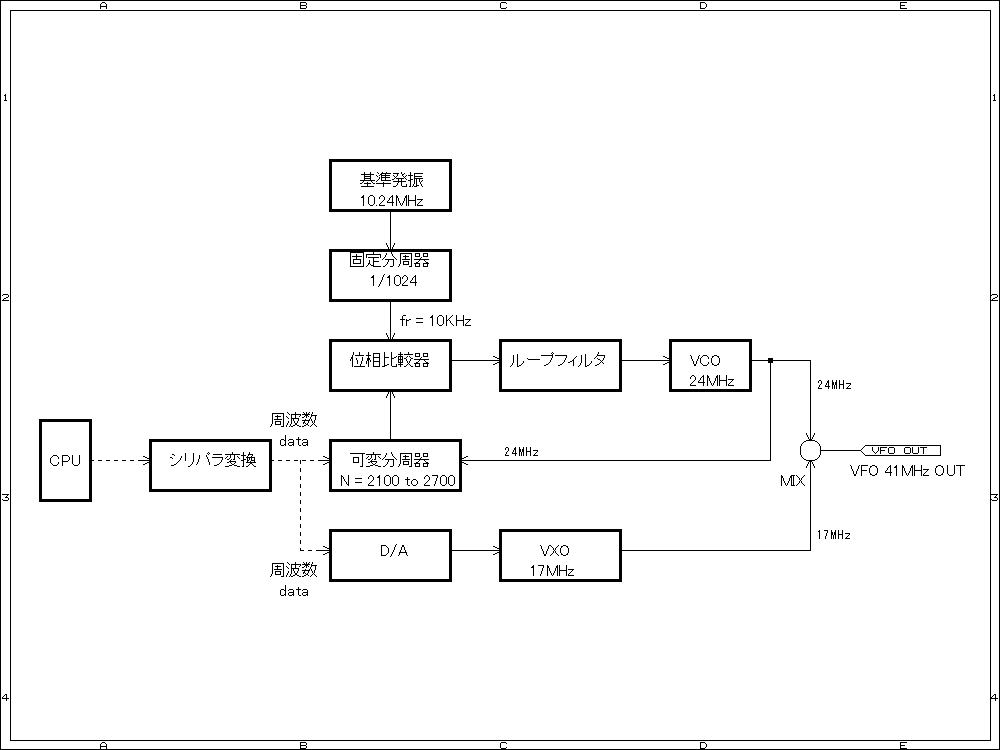

PLL部のブロック図を下記に示します。

PLL の 24 MHz の出力は、VXO の 17 MHz とM I X されて、41MHz 帯のVFO出力となります。

PLL のリファレンスクロック fr は、10KHz ですので、PLL出力も10KHz ステップでしか可変できません。

そこで、バリキャップで動作する17MHz VXO をCPU のD/A出力でコントロールし、この10KHz のあいだの周波数を細かく可変してVFOに必要な周波数分解能を得ます。

今回の製作では、CPU を8 ビット(256階調)で動作させますので10KHz / 256 ≒ 40 Hz ステップづつの可変としました。

PLL IC には、かなり古い IC ですがモトローラの MC145163P を使用しました。

この IC には、基準発振器、固定分周器、位相比較器、可変分周器の機能が含まれます。

ただ、可変分周器への分周数データは、パラレルデータ ( しかもBCD ) で入力しなければならない為、CPU で制御するには少々使いにくい ICでは、あります。

今回製作したPLL VFO のPLL部の回路図を下記に示します。

ループフィルタは、アクティブな完全積分器を使用したステップ応答LPFです。

ステップ応答としている為、このループフィルタを含むオープンループ特性は、基準発振 fr (= 10kHz ) に対して、計算上約-70dB程度ですので、PLL出力に含まれる10kHzのFM変調成分を充分減衰させることができます。

また、回路の位相余裕も計算上約60度程度となっていますので、ロックアップ時間もまずまずだと思います。

VCOは、クラップ発振回路です。L1 は、φ0.14UEW を空芯ボビンに巻いています。L1 ,C1 ,C2 ,C3 は、発振裕度と可変範囲を見ながらカット&トライで決定しました。広範囲に可変させようとすると発振裕度がなくなり、発振停止しやすくなるので、なかなか諸元の決定が難しいものです。

VCOの発振特性を下記に示します。

VCOの発振特性は、制御電圧に対して負の傾きとなっています。

これは、PLL IC M145163P のパッシブフィルタ用の制御端子(PD OUT)に反転増幅器を用いたアクティブフィルタを接続しているため、パッシブフィルタの場合とは、制御方向を逆にする必要があるためです。

回路図中でバリキャップをVccに接続しているのは、このためです。

それから、今回製作したVCOは、制御電圧が9V以上の領域で動作不安定となり、制御電圧に対する周波数の傾きが正となってしまいました。

このため、一旦PLLがこの正の傾きの領域に入り込んでしまいうと制御方向が逆になってこの領域から出られなくなってしまいます。

そこで、制御電圧が9V以上とならないようにグランド間に8Vツェナーを挿入しています。